You can learn 40+ pages vhdl code for mod 10 counter analysis in Doc format. The clock inputs of all the flip-flops are connected together and are triggered by the input pulses. 2364 x 1 MULTIPLEXER using 8 x 1 multiplexer Structural Mod 10 Up Counter Verilog with Test fixture. Ring Counter very similar to shift register. Check also: code and vhdl code for mod 10 counter Thus all the flip-flops change state simultaneously in parallel.

22Last time several 4-bit counters including up counter down counter and up-down counter are implemented in Verilog. Counter-examples Arithmetic-Circuits Analog Integrated Circuits -Analog electronic circuits is exciting subject area of electronics.

How To Create A Timer In Vhdl Vhdlwhiz Refer following as well as links mentioned on left side panel for useful VHDL codes.

| Topic: Vhdl mod 10 counter decade counter. How To Create A Timer In Vhdl Vhdlwhiz Vhdl Code For Mod 10 Counter |

| Content: Learning Guide |

| File Format: Google Sheet |

| File size: 1.8mb |

| Number of Pages: 23+ pages |

| Publication Date: January 2017 |

| Open How To Create A Timer In Vhdl Vhdlwhiz |

|

Write VHDL code for 3-bit up counter.

22Design of MOD-6 Counter using Behavior Modeling Style VHDL Code. 7My state machine works like this. 19Modulus counters or simply MOD counters are defined based on the number of states that the counter will sequence through before returning back to its original value. Its not a recognized clocking method. I trying to write a MOD-5 counter that counts like this 000001010110111000. Vhdl cam content addressable memory.

Vhdl Clock Problem While Creating Modulo 16 Counter Stack Overflow When I simulate the code this is the count I get 000001010011100101110111000.

| Topic: 29These examples use the rising edge of clk. Vhdl Clock Problem While Creating Modulo 16 Counter Stack Overflow Vhdl Code For Mod 10 Counter |

| Content: Answer |

| File Format: DOC |

| File size: 1.6mb |

| Number of Pages: 35+ pages |

| Publication Date: April 2019 |

| Open Vhdl Clock Problem While Creating Modulo 16 Counter Stack Overflow |

|

Design C 1 Modulo 10 Up Counter Using The Chegg The testbench VHDL code for the counters is also presented together with the simulation waveform.

| Topic: 9Counters are sequential circuits that employ a cascade of flip-flops that are used to count something. Design C 1 Modulo 10 Up Counter Using The Chegg Vhdl Code For Mod 10 Counter |

| Content: Answer |

| File Format: Google Sheet |

| File size: 5mb |

| Number of Pages: 23+ pages |

| Publication Date: January 2017 |

| Open Design C 1 Modulo 10 Up Counter Using The Chegg |

|

Introduction To Vhdl Structure Model Vhdl Code Entity In this VHDL project the counters are implemented in VHDL.

| Topic: When the counter reaches 9 next count value will be 0 then the 4-bit counter wraps at 9 1001 not at 15 1111 as a 4-bin binary counter does. Introduction To Vhdl Structure Model Vhdl Code Entity Vhdl Code For Mod 10 Counter |

| Content: Answer |

| File Format: PDF |

| File size: 725kb |

| Number of Pages: 22+ pages |

| Publication Date: August 2019 |

| Open Introduction To Vhdl Structure Model Vhdl Code Entity |

|

Pdf Design And Implementation Of Mod 6 Synchronous Counter Using Vhdl Semantic Scholar First we will take a look at their logic circuits.

| Topic: On reset it comes to s0 and then if start 1 goes to s2 and in this state I want it to stay there for 12 clock cycles 12 clock cycle delay and then goes to s2 and done 1 here and then back to s0. Pdf Design And Implementation Of Mod 6 Synchronous Counter Using Vhdl Semantic Scholar Vhdl Code For Mod 10 Counter |

| Content: Synopsis |

| File Format: Google Sheet |

| File size: 5mb |

| Number of Pages: 26+ pages |

| Publication Date: April 2018 |

| Open Pdf Design And Implementation Of Mod 6 Synchronous Counter Using Vhdl Semantic Scholar |

|

1 Write The Vhdl Code To Describe A Modulo 10 Chegg EVEN ODD COUNTER Behavioral 3-Bit UP DOWN Counter Structural.

| Topic: Vhdl variable flip flop. 1 Write The Vhdl Code To Describe A Modulo 10 Chegg Vhdl Code For Mod 10 Counter |

| Content: Answer |

| File Format: DOC |

| File size: 1.7mb |

| Number of Pages: 40+ pages |

| Publication Date: November 2019 |

| Open 1 Write The Vhdl Code To Describe A Modulo 10 Chegg |

|

3 1 Designing A Modulo 10 Counter In This Experiment Chegg Not sure why the simulation goes to 5.

| Topic: Under the assumption you want the counter to go from 0 to 9 and rollover this. 3 1 Designing A Modulo 10 Counter In This Experiment Chegg Vhdl Code For Mod 10 Counter |

| Content: Learning Guide |

| File Format: Google Sheet |

| File size: 1.8mb |

| Number of Pages: 11+ pages |

| Publication Date: May 2017 |

| Open 3 1 Designing A Modulo 10 Counter In This Experiment Chegg |

|

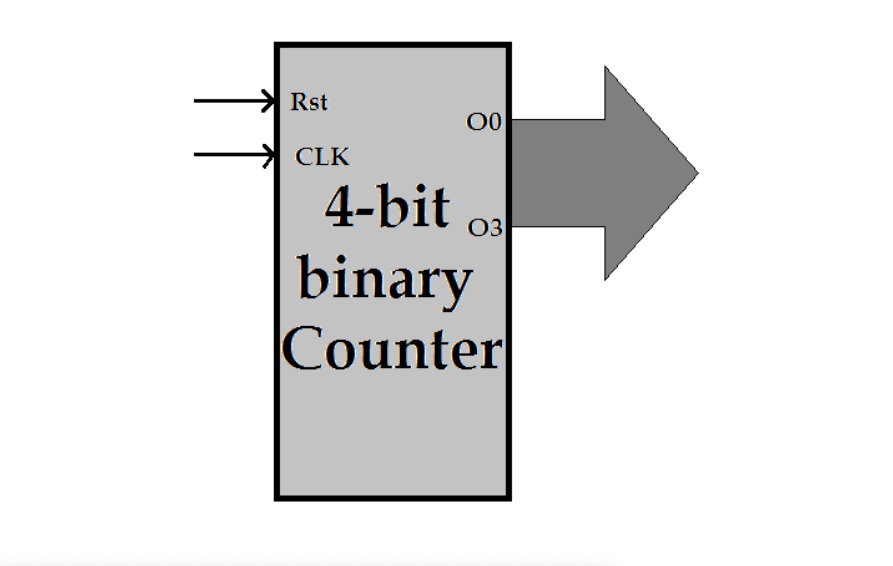

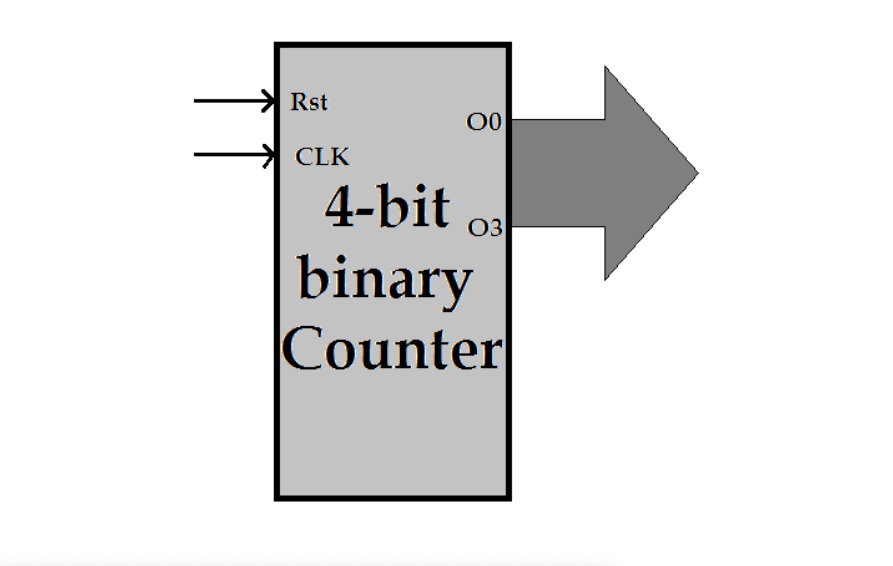

Vhdl Tutorial 19 Designing A 4 Bit Binary Counter Using Vhdl Making a modulo 10 counter.

| Topic: February 13 2014 by shahul akthar. Vhdl Tutorial 19 Designing A 4 Bit Binary Counter Using Vhdl Vhdl Code For Mod 10 Counter |

| Content: Explanation |

| File Format: Google Sheet |

| File size: 1.6mb |

| Number of Pages: 11+ pages |

| Publication Date: October 2019 |

| Open Vhdl Tutorial 19 Designing A 4 Bit Binary Counter Using Vhdl |

|

Vhdl Implementation Of Lookup Table Download Scientific Diagram ADD COMMENT FOLLOW SHARE EDIT.

| Topic: 1756 nareshdobal 4 comments Email This BlogThis. Vhdl Implementation Of Lookup Table Download Scientific Diagram Vhdl Code For Mod 10 Counter |

| Content: Analysis |

| File Format: DOC |

| File size: 2.6mb |

| Number of Pages: 8+ pages |

| Publication Date: January 2020 |

| Open Vhdl Implementation Of Lookup Table Download Scientific Diagram |

|

Write A Plete Vhdl Description For An Active High Chegg Vhdl cam content addressable memory.

| Topic: I trying to write a MOD-5 counter that counts like this 000001010110111000. Write A Plete Vhdl Description For An Active High Chegg Vhdl Code For Mod 10 Counter |

| Content: Answer |

| File Format: Google Sheet |

| File size: 2.6mb |

| Number of Pages: 6+ pages |

| Publication Date: November 2017 |

| Open Write A Plete Vhdl Description For An Active High Chegg |

|

Introduction To Vhdl Structure Model Vhdl Code Entity 22Design of MOD-6 Counter using Behavior Modeling Style VHDL Code.

| Topic: Introduction To Vhdl Structure Model Vhdl Code Entity Vhdl Code For Mod 10 Counter |

| Content: Analysis |

| File Format: Google Sheet |

| File size: 6mb |

| Number of Pages: 50+ pages |

| Publication Date: June 2021 |

| Open Introduction To Vhdl Structure Model Vhdl Code Entity |

|

Design An 8 Bit Modulo 256 Binary Counter Vhdl Chegg

| Topic: Design An 8 Bit Modulo 256 Binary Counter Vhdl Chegg Vhdl Code For Mod 10 Counter |

| Content: Summary |

| File Format: Google Sheet |

| File size: 5mb |

| Number of Pages: 13+ pages |

| Publication Date: December 2019 |

| Open Design An 8 Bit Modulo 256 Binary Counter Vhdl Chegg |

|

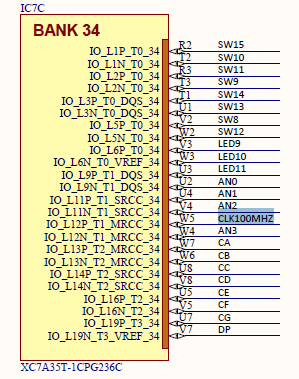

Its definitely easy to prepare for vhdl code for mod 10 counter Vhdl clock problem while creating modulo 16 counter stack overflow vhdl tutorial 19 designing a 4 bit binary counter using vhdl how to create a timer in vhdl vhdlwhiz vhdl implementation of lookup table download scientific diagram design an 8 bit modulo 256 binary counter vhdl chegg lesson 78 example 50 modulo 5 counter vhdl programs few examples write a plete vhdl description for an active high chegg

0 Comments